2009年6月1-3日 総研大実習 テーマA6

# シリコンセンサーの基礎

2009年6月1日 KEK 坪山 透

## はじめに

シリコンセンサーは現在および将来の素粒子実験で最も重要な役割を果たす。写真は「シ

リコンストリップセンサー」と 呼ばれ、300μm厚のシリコン板 に50 μm おきに細長い電極を取 り付け、素粒子がそのセンサー を通り抜けたときに発生するごく

1cm x 8 cm x 0.3 mm のシリコンストリップセンサー

少ない電荷を集めて、粒子の通過位置を測定する。シリコンセンサーの両面に電極を設けることで、2次元情報 XY の測定が可能になる。典型的なシリコンセンサーでは、面内の

通過位置を表・裏それぞれ 10 μm 程度の精度で測点することができる。 さらに カン

度で測定することができる。さらに、センサーの置く位置 Z を精度よく決めることで、素粒子通過位置の XYZ の情報を得ることができる。2 枚以上のセンサーを集めれば、粒子の軌道の測定が可能になる。磁場中を走る荷電粒子はらせん運動をする。

3 枚以上のセンサーを用いて、運動の曲率

半径を測ることで、粒子の進む方向と運動量の

測定を行う。複数の粒子が一つの検出器を通り抜ける場合、従来の検出器では軌跡が 1 cm 程度離れている必要があるが、シリコンストリップセンサーの場合は、50 μm の間隔

で電極が作ってあるおかげで、きわめて接近 した粒子を分離することが可能になる。

CERN で準備が進んでいる LHC 実験の CMS 測定器や ATLAS 測定器には100 平方メート ル以上のシリコンセンサーが用いられ、その 中を通り抜ける粒子の発生位置、進行方向、 運動量が極めて高い精度で測定が行われる。 この演習ではこうした半導体検出器の基礎を 学ぶ。

### 半導体の性質

シリコンは元素の周期律表4族に含まれ4本の結合手を持つので、純粋な結晶はダイヤモンドと同じ構造になる。従って、純粋なシリコンの結晶はほとんど電気を通さない。しかし結晶中にごく少量の不純物を加えることで、思いも寄らぬ性質が生まれ、それが現在の高

度なエレクトロニクス社会の根本になっている。半導体が高感度の光・素粒子の検出器になるのも重要な性質のひとつと言える。こうした性質を理解するために、半導体検出器の原理を学習しよう。シリコンの性質といくつかの式をまとめておく。

| シリコンの性質                       |                                                                                                                                                             |

|-------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 密度                            | 2.33 g/cm <sup>3</sup>                                                                                                                                      |

| 純粋シリコンの常温でのキャリア濃度 $n_{\rm i}$ | 1.45 10 <sup>10</sup> cm <sup>-3</sup>                                                                                                                      |

| バンドギャップエネルギー E <sub>G</sub>   | 1.1 eV                                                                                                                                                      |

| 電子・ホール対を作るために必要なエネルギー         | 3.6 eV                                                                                                                                                      |

| 電子易動度 με                      | 1400 (cm/s)/(V/cm)                                                                                                                                          |

| ホール易動度 $\mu_{ m h}$           | 500 (cm/s)/(V/cm)                                                                                                                                           |

| 誘電率 $\varepsilon$             | 1.05 pF/cm                                                                                                                                                  |

| 抵抗率 $\Omega$ (不純物濃度 $N_n$ )   | $1/e\mu_eN_n$                                                                                                                                               |

| 内蔵電位 $arphi_{ m bi}$          | $(kT/e)\ln(N_{\rm p}N_{\rm n}/n_{\rm i}^2)$                                                                                                                 |

| 空乏層厚み d                       | $\sqrt{2\varepsilon(V_{\text{bias}} + \varphi_{\text{bi}})/eN_{\text{n}}} = \sqrt{2\Omega\varepsilon\mu_{\text{e}}(V_{\text{bias}} + \varphi_{\text{bi}})}$ |

| 静電容量 C (面積 S 厚みd)             | $\varepsilon S/d$                                                                                                                                           |

| ブレークダウン (降伏) 電界               | 3 • 10 <sup>5</sup> V/cm                                                                                                                                    |

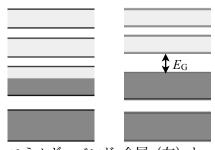

#### エネルギーレベルとバンド構造

水素原子の電子がもつエネルギーレベルはとびとびの値 に離散化されている。ところが、シリコンのような結晶 中の電子のエネルギーレベルは、多数のエネルギーレベ ルが混合してエネルギーバンド(帯)を形成する。その なかで、電子はエネルギーの低い準位から埋まってゆ く。金属の場合は、ひとつのバンドのなかに、電子が充

満しておらず、その中の電子は室温で励起され、励起された電子は結晶中を自由に動くこ

とができる。それが電気伝導の原因となる。電子が完全に充満しているバンドと電子がいないバンドに別れている結晶もある。電子は許容された以外のエネルギーをとり得ない。 その間のエネルギーギャップ  $(E_G)$  が大きい場合は、室温では電子が励起されず電子は充満バンドに固定され電流が流れることはできない。

シリコンなどの半導体の場合も絶縁体と同じバンド構造を持っているが、 $COE_G$ が $1.1\,eV$  (電子ボルト)程度になっている。電子があるエネルギーをもつ確率はフェルミ分布関数

エネルギーバンド: 金属(左)と、 絶縁体・真性半導体(右)

$$F(E) = \frac{1}{e^{-\frac{E - E_{\rm F}}{kT}} + 1}$$

で表される。k はボルツマン定数、T は温度で室温の場合はkT=0.026電子ボルト (eV) となる。 $E_F$  はフェルミエネルギーを表す。純粋なシリコンでも、ほとんど電子は励起されず、電気伝導率は非常に小さい。これだけでは物理的にも応用面でもあまり興味深くないが、半導体に少量の不純物を加えると、様相が全く変化する。

## PN接合

リン (P) やヒ素 (As) などのV族元素は共有結合手を 5本持つため、 これらがシリコン結晶中にある と、Si 原子と結合できない電子が発生する。この 電子は極めて低いエネルギーで励起されてシリコン結晶中を移動できるようになる。バンド図では、 伝導帯の 0.02 eV 程度下の準位となり、室温では、その電子はほぼ完全に伝導帯に移り自由に動くことができるので、自由電子と呼ばれる。こうしたシリコンを n 型シリコンと呼び、この不純物原子をドナー呼ぶ。一方、シリコンにホウ素 (B)などの川族の

P型 (左) N型 (右) シリコンのバンド図 鎖線(青) は不純物によるアクセプター・ ドナーのエネルギーレベル。点線 (赤) は フェルミエネルギーを示す。

元素をドープすると、結晶中のSi 原子と結合できない空の軌道ができる。Si の電子がここ

に移ると、その空の状態は、あたかも正の電荷を持つ電子のようにシリコン中で運動する。「ホール(正孔)」と呼ばれる。この場合、ホウ素原子をアクセプター呼び、シリコンを P型と言う。ホール・自由電子を総称してキャリア(担体)などと呼ぶ。N(P)型半導体中の電子(ホール)を多数キャリア、ホール(電子)を小数キャリアと呼ぶ。つぎに P型シリコンと N型シリコンを接合した場合を考える。接合面付近では電子・ホールは拡散(熱運動)により、電子が P型側、ホールが N型側に広がってゆく。そして、界面近傍ではホールと電子が衝突し、エネルギーを熱として放出しながら対消滅をする。これを「再結合」と呼ぶ。再結合がおこり、ホールと電子が中和し電子もホールもない領域が現れる。これを空乏(depletion)領域と呼ぶ。空乏

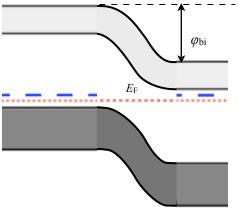

PN接合後のバンド図。境界付近はホールも電子もない空乏層になる。 P側のポテンシャルが増加し、P型シリコンのホール、N型シリコンの電子が移動できなくなる。 左右のポテンシャルの差がPN接合の内蔵電位(℘ы)である。

領域にはドナーとアクセプターの原子が残る。これらは、それぞれ正と負の電荷を持つため、接合面の左右に電位のアンバランスが生じる。 この電位差を内部電位  $\varphi$ bi と呼び次の式

2009年6月1-3日

$$\varphi_{\rm bi} = \frac{kT}{e} \ln \frac{N_{\rm p} N_{\rm n}}{n_{\rm i}^2}$$

で表され、通常 0.7 V 程度となっている。P側のホールとN側の自由電子は同じ $E_F$  になるが、 この  $\varphi_{\text{bi}}$  のが障壁となり反対側の結晶領域に拡散できなくなる。

## 空乏領域の性質

②空乏領域では電荷の移動が出来ない。したがって、絶縁体に見える。その誘電率 ( $\epsilon$ ) は シリコン本来が持つ誘電率1.05 pF/cmとなる。

©シリコン中を荷電粒子(陽子や $\pi^{\pm}$ など電荷を持った素粒子)が通り抜けると、クーロン力で結晶が励起され、軌跡  $1~\mu m$  あたり 80~2程度のホールと自由電子対が発生する。また励起エネルギー以上のエネルギーを持つ光子が入る場合もホールと自由電子対を生成することができる。空乏領域には他のホールや自由電子がほとんど存在していないため、電場が存在し、再結合がおこる前に長い距離を走ることができる。電荷が長い距離を走るので、結晶内に電流が発生したことになる。外部に増幅器を接続すれば粒子の通過が検出できる。空乏化していないシリコンでは、発生したホール・自由電子はすぐに再結合を起こす。空乏化していないシリコンは一種の導体であり、電界も小さく電荷が発生しても信号にならない。つまり半導体でセンサーを作る場合、「空乏領域の厚み」が性能を決めることになる。そこで、空乏層の厚みの計算をしてみよう。

# 空乏領域に関するモデル計算

面倒な計算をさけるためにモデルを簡単化する。

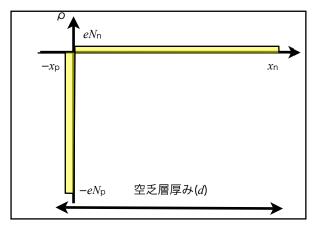

○ P型 N型シリコンの不純物濃度はそれぞれ 一定とする。

- ◎空乏化しているところは、シリコン結晶 に固定された不純物で電荷密度が決まる。

- ◎空乏化していない部分では電気伝導度が 大きく電場が 0 である。

x=0 が P型・N型シリコンの境界である。

上図のように、P型・N型シリコンでの空乏領域の広がりを $x_p$ ・ $x_n$ とする。シリコン全体の電荷は保存するので、 $N_p x_p = N_n x_n$ となる。ホールより自由電子の移動度のほうが大きい

ため、P型でなく N型半導体を用いる方がより優れた検出器が得られる。そこで主に N型 領域を空乏化することにする。 つまり  $x_n >> x_p$ を課す。そのめには、 $N_p >> N_n$  つまり、P型 シリコンの不純物濃度が非常に高い場合を考える。結晶内部の電荷分布を決めたので、電荷分布  $\rho(x)$  とポテンシャル  $\varphi(x)$  の関係を示す一次元ポワソン方程式を解けばシリコン内 の電位が決まる。

$$d^2\phi / dx^2 = -\rho(x) / \varepsilon$$

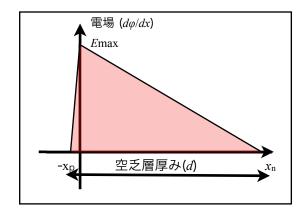

この式を 1 回積分して電場を求める。境界条件は空乏領域の外側  $(x<-x_p$  と  $x>x_n)$  で  $d\varphi(x)/dx=0$ である。

$$d\varphi(x)/dx = 0 \qquad (x < -x_p)$$

$$d\varphi(x)/dx = -x(-eN_p)/\varepsilon + E \max \qquad (-x_p < x < 0)$$

$$d\varphi(x)/dx = -x(-eN_n)/\varepsilon + E \max \qquad (0 < x < x_n)$$

$$d\varphi(x)/dx = 0 \qquad (x_n < x)$$

となる。 $E\max = ex_pN_p/\varepsilon = ex_nN_n/\varepsilon \simeq edN_n/\varepsilon$  となる。

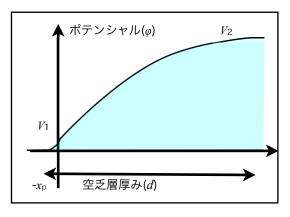

さらにこの式を積分すると、ポテンシャル $\varphi(x)$  が求まる。

$$\varphi(x) = 0$$

$\varphi(x) = -(1/2) x^2(-eN_p)/\varepsilon + x E \max + V_1$

$\varphi(x) = -(1/2) x^2(-eN_n)/\varepsilon + x E \max + V_1$

$\varphi(x) = V_2$

$(x < -x_p)$

$(-x_p < x < 0)$

$(0 < x < x_n)$

$(x < -x_p)$

$(x_n < x_n)$

これを解くと、

$$V_{1} = 1/2 x_{p}^{2} e N_{p} / \varepsilon$$

$$V_{2} = 1/2 x_{p}^{2} e N_{p} / \varepsilon + 1/2 x_{n}^{2} e N_{n} / \varepsilon = 1/2 x_{n}^{2} e N_{n} / \varepsilon (1 + N_{p} x_{p}^{2} / N_{n} x_{n}^{2})$$

$$= 1/2 x_{n}^{2} e N_{n} / \varepsilon (1 + x_{p} / x_{n}) \approx d^{2} e N_{n} / 2\varepsilon$$

となる。 $V_2$  は内部電圧  $\varphi_{\text{bi}}$  と外部から加えるバイアス電圧  $V_{\text{b}}$  の和である。空乏層の厚み d は、バイアス電圧の平方根に比例する。

#### 空乏化電圧

シリコン内で発生する電荷を効率的に測定するためには、シリコン検出器の厚みを完全に空乏化させる必要がある。その電圧を(完全)空乏化電圧  $V_{\rm d}$  と呼ぶ。PN 接合の空乏領域を積極的に用いる検出器を PIN (P-intrinsic-N) ダイオードと呼ぶ。 同じ空乏層厚を得るために必要なバイアス電圧は低ければそれだけ検出器の使用が楽になるので、より  $N_{\rm n}$  の小さなシリコンを使う必要がある。 実際に用いられるシリコンセンサーでは、使用目的に従って、空乏層の長さは数  $\mu$ m から数  $\mu$ m のものが用いられる。

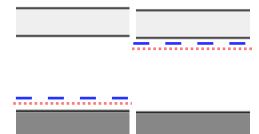

### 逆バイアスと順バイアス

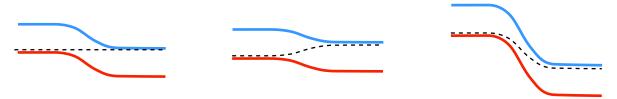

次の図を用いてPINダイオードに電圧を加えた場合の状況をもう少し詳しく考える。左図は外部に電源をつながない場合で、P側のホールとN側の電子の  $E_F$  は同じになっている。しかし  $\varphi_{bi}$  により電流は流れない。中図はN側に一、P側に+の電圧を加えた場合で、P側のホールとN側の電子は反対側に流れることが出来る。反対側の領域に流れ込むとそこの

#### 2009年6月1-3日

多数キャリアとの間で再結合をおこし消滅をする。その結果外部の電圧が存在する限り PN接合には電流が流れ続ける。再結合で開放されるエネルギーはシリコンを発熱させる。右図は逆方向に電圧を掛けた状態でポテンシャルの障壁は左図よりさらに大きくなる。上に述べたように、この電圧のおかげで空乏領域を増やすことになる。

右からバイアス無し、順バイアス状態、逆バイアス状態のエネルギーを示す。赤線・青線は充満帯と導電帯を示す。中央の点線はフェルミエネルギー (F<sub>G</sub>)を示す。

### シリコンの抵抗率と不純物濃度

N 型シリコンに電場 E を掛けると、シリコン中の自由電子は  $E_{\mu e}$  の速度で移動する(移動度の定義)。従って不純物濃度  $N_n$  のシリコン場合の電流密度 j は $-E_{e\mu e}N_n$  となる。抵抗率  $\Omega$  はその係数の逆数である。

$$\Omega = 1/(e\mu_e N_n)$$

実験で簡単に測定が直接できるのはシリコンの  $N_{\rm n}$ ではなく  $\Omega$  なので  $\Omega$  を用いて空乏層 厚みを計算する方が実用的である。 $N_{\rm n}$ =  $1/(\Omega e \mu_{\rm e})$  より、  $V_2$ =  $V_{\rm b}$ + $\varphi_{\rm bi}$ =  $d^2/(2\Omega \epsilon \mu_{\rm e})$ 。したがって、

$$d = \sqrt{2\Omega\varepsilon\mu_{\rm e}(V_{\rm bias} + \varphi_{\rm bi})}$$

となる。

### ダイオードの接合容量

最初に述べたようにシリコンが空乏化すると、空乏層の厚みdに応じた静電容量C

$$C = \varepsilon S/d$$

が測定される。d はバイアス電圧に依存するが、完全空乏化電圧  $V_d$  以上では d はシリコンの厚みになり、静電容量が変化しなくなる。静電容量のバイアス電圧依存性を測定することで、全空乏化電圧を測定することができる。

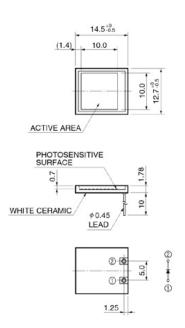

### シリコンPINフォトダイオードの構造

PINフォトダイオードは主に可視光を検出するために使われる。最初に述べたようにシリコンのバンドギャップ  $E_G$ は、1.1 eV であるが、平均 3.6 eV の光のエネルギーで 1 電子ーホール対が発生する。

問題: 1.1 eV は光の波長ではどの位か?それは 紫外線か 、可視光か、赤外線か? ただし  $E=vh=hc/\lambda$ 、プランク定数  $h=6.63\cdot 10^{-34}\,\text{J}\,\text{sec}=4.14\ 10^{-15}\,\text{eV}\,\text{sec}$  とする。

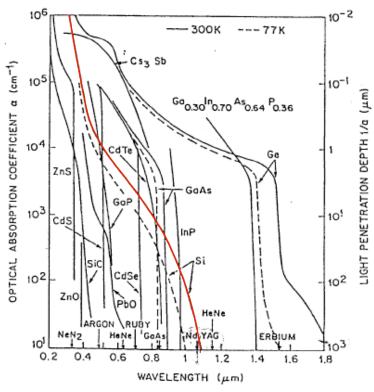

可視光はE<sub>G</sub>を越えるエネルギーを持ち、シリコン中では数 μm 走る間にすべて吸収され

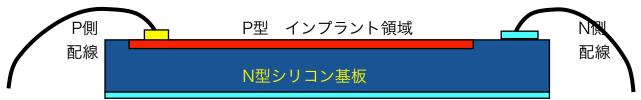

る。したがって、可視光を高い 効率で測定するためには、シリ コンの表面の数 µm だけ高感度 ならば十分である。通常のIC技 術はシリコンの表面から 1-2 μm の深さにCMOSトランジスター などの構造を作る。IC技術で製 造した CCD や CMOS カメラ が高性能を発揮するのは、 視光がシリコン表面で吸収され る」という特別な事情のおかげ と言える。この演習で使うPIN フォトダイオードの構造の簡略 化した図を下に示す。本課題で 試験する PIN ダイオードは抵抗 率 4 kΩ cm・厚み 300 μmの N 型 シリコン(青)から作られてお り、 面積は 1 cm<sup>2</sup>である。P領域

S. M. Sze "Physics of Semiconductor Devices", 1990

は機械的接合ではなく、ホウ素などの原子を高い電圧 (数10-100 kV) で加速して、シリコン表面に**打ち込む**(インプラント)ことで作られる。インプラントした原子を シリコン結晶となじませる (活性化)ためにシリコンの板は数 100  $^{\circ}$   $^{\circ}$  で加熱される。インプラントの深さは 1  $^{\circ}$   $^{\circ}$  程度である。これまでに述べたように打ち込むアクセプター濃度は非常に高いのでP領域の電気伝導率は高い。そこで、バイアス電圧を掛けたり、信号を取り出したりするためには、P 領域の一部にアルミを蒸着し(黄色)配線をすれば十分である。N 側はシリコン板の裏側や、表面の一部にアルミ(空色)を蒸着して信号を取り出す。ここにバイアス電圧を掛けることで、P型の境界面から空乏層が発達し、「全空乏化電圧」に達したところで、Nの基盤はほぼ厚みいっぱい空乏化する。

### 練習問題

典型的な PIN フォトダイオードは 抵抗率  $4 \text{ k}\Omega \text{ cm}$ ・厚み  $300 \text{ }\mu\text{m}$ の N 型シリコン基盤を用い、P領域は表面からおよそ1  $\mu\text{m}$ の深さに硼素をインプラントして作られる。

- (1) 不純物濃度 N₁ をもとめよ。

- (2) 完全空乏化するために必要なバイアス電圧 (V<sub>d</sub>) をもとめよ。

- (3) 面積は  $1 \text{ cm}^2$ だとして、空乏化後の静電容量  $C_d$  をもとめよ。

- (4)  $N_n$ は(1)でわかった。シリコンの厚みより  $x_n=300~\mu m$ 、不純物打ち込みの深さはたかだか  $x_p=1~\mu m$  である。ここから  $N_p$  (の下限)を求めよ。

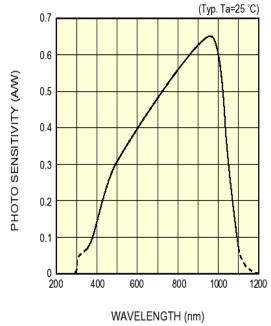

- (5) 光がすべてPインプラント領域で吸収される場合、空乏層にで電子ーホール対が発生しないので、信号が出なくなる。その波長はどの程度か。(上のグラフをみて考えよ)

# 高性能センサーのためには空乏化が必要である

- (1) 光検出でも素粒子通過でも実験では微少信号を測定する場合が多い。信号を観察するためには、電子回路で増幅しなくてはならない。ところが熱雑音の理論により「回路の静電容量が大きいと原理的に雑音が増える」ことが知られている。センサーを全空乏化すると静電容量が減少するので、それだけ測定される雑音が減る。

- (2) 電荷を持つ素粒子がシリコンを通過するときは、軌跡に沿って電子一ホール対が生成する。上に述べたとおり測定できる空乏層に発生した信号のみである。つまり、空乏層の厚みに比例して信号がふえる。したがって、空乏層の厚みをシリコンの厚みまで増やすことが重要である。 それに対し、可視光はセンサー表面で吸収されるので、空乏層が数μm 以上有っても信号は増えない。

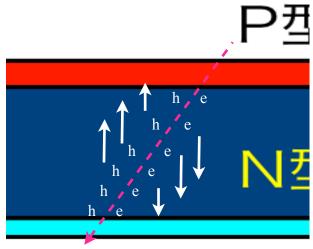

荷電粒子がシリコン中を通過すると、軌跡に沿って電子・ホール対が発生し、空乏層中をそれぞれN・Pの方向に進む。

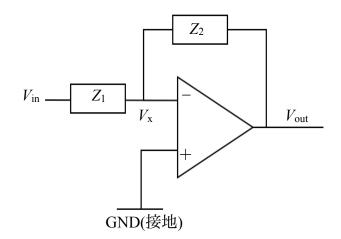

## OPアンプ回路

ここでシリコンセンサーの評価に用いるOPアンプを説明する。OPアンプはインピーダンスがほぼ無限大の+と-の入力を持ち、ほぼ無限大の増幅率を持つ電圧増幅回路である。動作を単純化すると、次のようなフィードバック回路を考えた場合、 $V_x$  が0になるように増幅器は振る舞う。

$V_{\rm x}$ =(( $V_{\rm in}/Z_1$ )+( $V_{\rm out}/Z_2$ ))/( $1/Z_1$ + $1/Z_2$ )=( $V_{\rm in}Z_2$ + $V_{\rm out}Z_1$ )/( $Z_1$ + $Z_2$ ) かつ  $V_{\rm x}$ =0 より、

$V_{\text{out}} = -(Z_2/Z_1)V_{\text{in}}$

となる。 $Z_1$  が 0 の場合は  $V_x=V_{in}=0$  となるが、この場合は「電流増幅回路」になり、

$$V_{\text{out}} = -Z_2 i_{\text{in}}$$

となる。  $Z_2$  が純粋な抵抗 Rなら $V_{\text{out}} = -I_{\text{IN}}R$  の電流増幅器、 $Z_2$  がコンデンサー C の場合は電荷積分器となる

$$V_{\text{out}} = -\frac{1}{C} \int I_{\text{IN}} dt$$

センサーから出てくる信号は「電荷」である場合が多いので、検出回路の初段には 電荷 積分回路による信号処理が多く行われる。回路図には書いてないが、OPアンプには電源 が必要である。電源回路からのノイズを落としたり、増幅を安定にするため、ICの電源ピ ンとグラウンドの間には大容量のコンデンサを置くのが普通である。

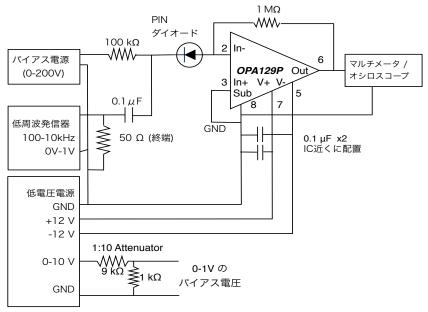

# 演習課題

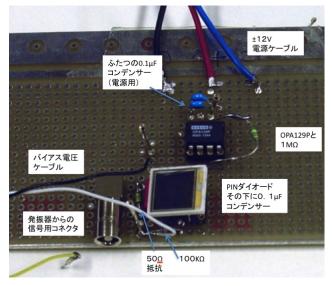

1) PINフォトダイオード評価回路を自作する。オペアンプは OPA129P を用いる。このアンプの特徴は入力に流れ込む電流が少ないことで、今回のような微少電流の精密測定に向いている。まず回路図・写真を参考に努力して完成させよう。半田付けのヤケドにはくれぐれも注意。ケーブルの色は黒 (GND)・赤 (+12 V)・青 (-12V)・黒 (細: GND)・白 (細: バイアス) などと決める。基盤が完成したら動作試験を行う。必要な電流は1 mA程度なので、電源装置の電流リミッターを 0.01 A に設定しておく。配線に誤りがあってもIC が壊れることを防ぐ。 実は試作回路は発信してしまった。外来の電子雑音を遮蔽するために、全体をアルミフォイルで覆うなどの工夫も必要になるかもしれない。このような対策は実験中に行う。

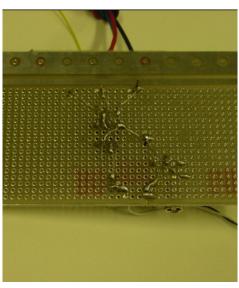

上記回路の試作品。オシロスコープで測定するためのポートも半田付けする。右側は裏側から見たもの。

2009年6月1-3日

- 2) ダイオードに順バイアス・逆バイアスをかけて、直流特性を測る。順方向には  $0.5\,\mathrm{V}$ まで、逆方向には予想される空乏化電圧の  $1.5\,\mathrm{G}$ まで電圧をかける。  $0-200\,\mathrm{V}$  のバイアス電源は  $0\,\mathrm{V}$ 付近で不正確なので、  $1/10\,\mathrm{O}$  のアテニュエータで電源の電圧を下げて用いる。バイアス電圧は、  $100\,\mathrm{k}\,\Omega$  抵抗の電源側(回路図では左側)で測る。 センサーにかかる電圧は電源電圧から( $i*100\,\mathrm{k}\Omega$ )を引いたものである。PINフォトダイオードは高感度光検出器なので、測定時にはきちんと遮光をすること。そのために黒ビニールも準備する。

- 3) ダイオードに逆バイアス電圧を掛けながら、静電容量を測る。バイアス電圧を変化させながら、空乏化が予想通り起こるかをしらべる。バイアス電圧の範囲は2) と同じでよい。 周波数 F・電圧 V の正弦波をコンデンサー C に掛けたとき、C に流れる電流iは

$i=2 \pi FCV$

で表される。その電流をOPアンプ回路で増幅する。オシロスコープで、正弦波の振幅を測ることで、Cを推定することが可能になる。交流電源の電圧はバイアス電圧より十分低いことが重要。横軸をバイアス電圧 V・縦軸を $1/C^2$ でプロットするとわかりやすい。既知のコンデンサー 100~pF 程度を用いて

4) バイアスをかけたフォトダイオードの信号をオシロスコープで観察しながら、受光面に光を当てて、観察する。

# 考察

- A) 演習課題2)・3) の測定結果から何が言えるか?

- B) 測定精度を検討する。バイアス電圧の精度、測定される電流・静電容量の精度はどの位か?

- C)実験ノートをきちんとつけること。日付・時間・天候などの情報が思わぬ役に立つことがある。

- D)レポート2-3枚にまとめる。

# 参考文献

- 1. 石原宏 岩波講座物理の世界物質科学の発展<4>半導体エレクトロニクス

- 2. S. M. Sze "Physics of Semiconductor Devices", 1990

# 付録

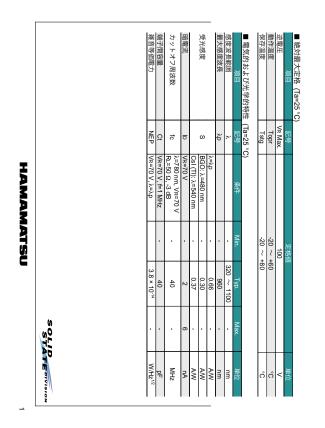

# S8650カタログ(浜松ホトニクス)

Difet is a registered trademark of Texas Instruments.

All other trademarks are the property of their respective owners

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

# OPA129P カタログ (Texas Instruments)

Burr-Brown Products from Texas Instruments

**OPA129**

SBOS026A - JANUARY 1994 - REVISED APRIL 2007

# Ultra-Low Bias Current Difet **OPERATIONAL AMPLIFIER**

CHROMATOGRAPHY PHOTODETECTOR PREAMPS **APPLICATIONS**

LOW OFFSET: 2mV max

● ULTRA-LOW BIAS CURRENT: 100fA max

- ELECTROMETER AMPLIFIERSMASS SPECTROMETERS

- pH PROBE AMPLIFIERS

- ION GAGE MEASUREMENT

# ₩ 30kΩ Substrate 8 e e < 01 ≨ ~

Therma DIP-8 SO-8

input bias current by a factor of 10 to 100. Very low input bias current can be achieved without resorting to small-geometry FETs or CMOS designs which can

suffer from much larger offset voltage, voltage noise,

# DESCRIPTION

PLASTIC DIP AND SO PACKAGES ● LOW NOISE: 15nV/√Hz at 10kHz

■ HIGH OPEN-LOOP GAIN: 94dB min ▶ LOW DRIFT: 10µV/°C max

SO-8 package. Using advanced geometry dielectrically-isolated FET (*Difer*) inputs, this monolithic conventional monolithic FETs. This reduces Diffet fabrication eliminates isolation-junction leakage current—the main contributor to input bias current with amplifier achieves a high performance level. operational amplifier offered in an 8-pin PDIP and The OPA129 is an ultra-low bias current monolithic

OPA129 is available in 8-pin DIP and SO packages, specified for operation from -40°C to +85°C. even with the surface-mount package version. that occurs with other op amps. Pins 1 and 4 have no internal connection, allowing circuit board guard traces— The OPA 129 special pinout eliminates leakage current drift, and poor power-supply rejection.

Simplified Circuit

TEXAS INSTRUMENTS www.ti.com

# **SPECIFICATIONS**

ELECTRICAL

At  $V_S = \pm 15V$  and  $T_A = +25$ °C, unless

| IMPUT ORFSET COLREINT |

|-----------------------|

|                       |

recovery is defined as the time required for the output to return from saturation to linear operation following the removal of a 50% input

°C €

OPA129 SBOS026A

# OPA129 SBOS026A

|                |              | 0      |     | Pulse \$ | Shift (d | degree | 9S)      |      |                                     |

|----------------|--------------|--------|-----|----------|----------|--------|----------|------|-------------------------------------|

|                |              |        |     |          | ply Re   |        |          |      |                                     |

|                | _            | 0 6    | 3 8 | 5 8      | 3 8      | 8 8    | 3 8      | \$ 8 | 5                                   |

|                | 10           |        |     |          |          |        | 1        |      | POWE                                |

|                | 100          |        |     | - h .    | 7        | $\neq$ |          |      | RSUPPL                              |

| Frecul         | <del>=</del> |        |     | E PR     | $\vdash$ |        | $\vdash$ |      | Y RE.                               |

| Frequency (Hz) | 10k          |        | /   | Ζ        | 7        | Z      |          |      | POWER SUPPLY REJECTION vs FREQUENCY |

|                | 100k         |        |     | /        | /        |        |          |      | FREC                                |

|                | ź            | $\neq$ |     |          | PSRR     |        |          |      | UENCY                               |

|                | 101          |        | ,÷  |          |          |        |          |      |                                     |

# At $T_A = +25^{\circ}C$ , +15VDC, unless otherwise noted. TYPICAL PERFORMANCE CURVES

#

NOTE: (1) Short circuit may be to power supply common at +25°C ambient.

# DISCHARGE SENSITIVITY **ELECTROSTATIC**

Top View

DIP/SO

ESD damage can range from subtle performance deg-radation to complete device failure. Precision inte-grated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet published specifications. Any integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precaulions. Failure to observe proper handling and installation procedures can cause damage.

ABSOLUTE MAXIMUM RATINGS

| PACKAGE  | INFORMATION(1) |                    |

|----------|----------------|--------------------|

| PRODUCT  | PACKAGE-LEAD   | PACKAGE DESIGNATOR |

| OPA129P  | DIP-8          | P                  |

| OPA129PB | DIP-8          | P                  |

| OPA129U  | 8-0s           | D                  |

| OPA129UB | SO-8           | D                  |

NOTE: (1) For the most current package and ordering information, see the Package Option Addendum at the end of this data sheet, or see the TI website at www.ti.com.

# CONNECTION DIAGRAM 중 <u>+</u> - ω ω 4 OPA Substrate Output ş