# 筑波大学数理物質科学研究科 物理学専攻 エレクトロニクス・データ処理 レポート課題

2016 年前期 新井 康夫 (yasuo.arai@kek.jp)

提出場所:自然系学系棟B棟221理学系事務室前レポートボックス

提出期限: 2016年8月12日(金) 16:00

(期限後、回答例を http://research.kek.jp/people/araiy/16lecture/ に載せます。)

### I. SPICE プログラムを使って下記の課題を行え。

SPICE を持っていない方は、LTspice IV (http://www.linear.com/designtools/software/#LTspice, Mac & Windows) 等の無料ソフトを用いて行って下さい。どうしても SPICE を行える環境が作れない方は II の問題を解いて下さい。III.は共通です。

\_\_\_\_\_

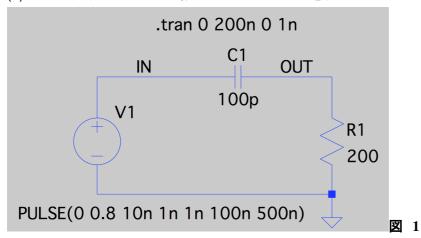

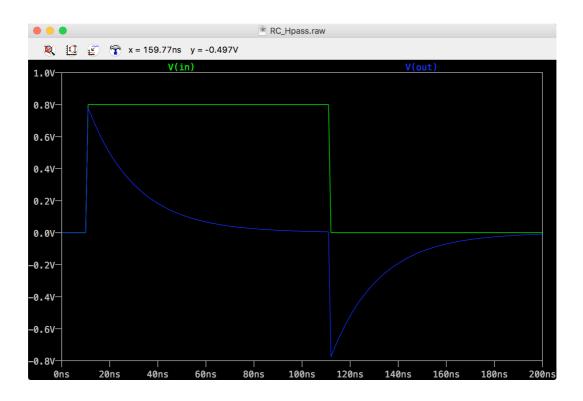

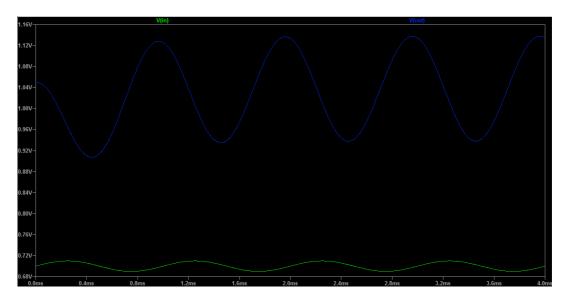

(a) 図1の回路に対して過渡解析シミュレーションを行い、INとOUTの波形を示せ。

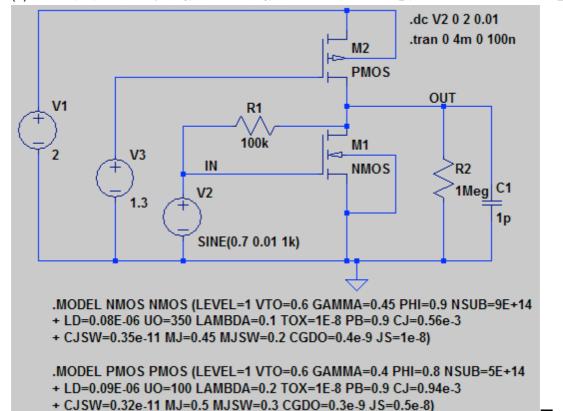

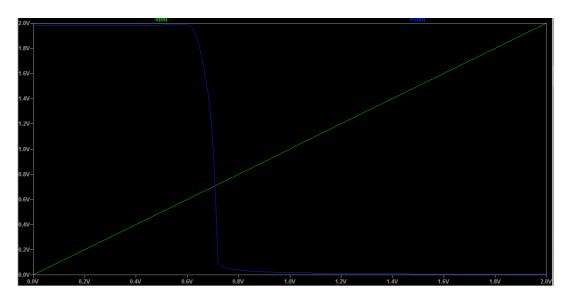

(b) 図2の回路に対して直流解析及び過渡解析シミュレーションを行い IN と OUT のグラフを示せ。

図 2

「参考」

.dc V2 0 2 0.01 .tran 0 4m 0 100n

M1 OUT IN 0 0 NMOS 1=0.5 w=600 M2 N001 N002 OUT N001 PMOS 1=2 w=50

C1 OUT 0 1p R1 IN OUT 100k R2 OUT 0 1Meg

V1 N001 0 2 V2 IN 0 SINE(0.7 0.01 1k) V3 N002 0 1.3

.MODEL NMOS NMOS (LEVEL=1 VTO=0.6 GAMMA=0.45 PHI=0.9 NSUB=9E+14

- + LD=0.08E-06 UO=350 LAMBDA=0.1 TOX=1E-8 PB=0.9 CJ=0.56e-3

- + CJSW=0.35e-11 MJ=0.45 MJSW=0.2 CGDO=0.4e-9 JS=1e-8)

.MODEL PMOS PMOS (LEVEL=1 VTO=0.6 GAMMA=0.4 PHI=0.8 NSUB=5E+14

- + LD=0.09E-06 UO=100 LAMBDA=0.2 TOX=1E-8 PB=0.9 CJ=0.94e-3

- + CJSW=0.32e-11 MJ=0.5 MJSW=0.3 CGDO=0.3e-9 JS=0.5e-8) .end

(MODEL を入れずに LTSpice の Standard Transistor を選択した方がいました。このため、結果が異なり増幅されません)

VTO:  $V_{SB}$ がゼロのときのしきい値電圧 (単位: V) GAMMA: 基板バイアス効果係数 (単位:  $V^{1/2}$ )

$PHI: 2\Phi_F($ 単位: V)

TOX: ゲート酸化膜厚 (単位: m) NSUB: 基板不純物濃度 (単位: cm<sup>-3</sup>)

LD: ソース/ドレインの側壁拡散長 (単位: m)

UO: チャネル移動度 (単位: cm²/V/s)

LAMBDA: チャネル長変調係数 (単位: V<sup>-1</sup>)

$CJ: ソース/ドレイン底面の単位面積あたりの接合容量 (単位: <math>F/m^2$ )

CJSW: ソース/ドレイン側壁の単位長あたりの接合容量 (単位: F/m)

PB: ソース/ドレイン接合のビルトインポテンシャル (単位: V)

MJ: CJ の解析式の指数 (単位:なし)

MJSW: CJSW の解析式の指数 (単位:なし)

CGDO: 単位長あたりのゲート-ドレインのオーバラップ容量 (単位: F/m)

CGSO: 単位長あたりのゲート-ソースのオーバラップ容量 (単位: F/m)

JS: 単位面積あたりのソース-ドレインのリーク電流 (単位: A/m²)

## [DC 解析]

### [過渡解析]

-----

#### (SPICE を行えない方)

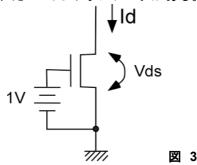

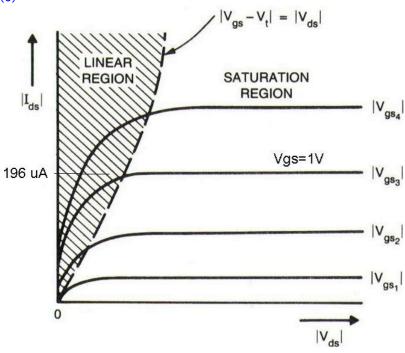

II-A. 図 3 のようにバイアスされた NMOS トランジスタがある。

- (a) このトランジスタが飽和領域で動作する為には、Vds は何 V 以上でなければならないか?

- (b) この時、Id の電流値はいくつになるか?

- (c) Id Vds の特性曲線を概略でグラフで示せ。

ただし、 $\mu_n$ =350 [cm²/V/sec],  $C_{OX}$ =7 [fF/ $\mu$ m²],  $V_{TH}$ =0.7 [V]、L=1 [ $\mu$ m], W=10 [ $\mu$ m]、チャネル長変調は無し( $\lambda$ =0) とする。

(a)  $Vds \ge Vgs-Vth = 1-0.7=0.3 V$

(b)

$$I_d = \frac{1}{2} \mu_n C_{ox} \frac{W}{L} (V_{gs} - V_{th})^2 = \frac{1}{2} \cdot 350 \cdot (7E - 15 \times 1E8) \cdot \frac{10}{1} \cdot 0.3^2$$

= 1.1×10<sup>-4</sup> = 110 [uA]

(c)

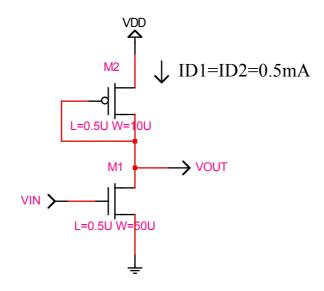

II-B. 図 4 に示したソース接地回路があり、 $(W/L)_1$ =50/0.5,  $(W/L)_2$ =10/0.5, Vth1=0.7 V, Vth2=-0.8Vかつ ID1=ID2=0.5mA とし、その他の条件は II-A と同じとする。

- (a) M1 及び M2 の gm の値を求めよ。

- (b) 電圧増幅率を求めよ。

図 4

$$ID1 = \frac{1}{2} \mu_n C_{ox} \frac{W}{L} (V_{gs} - V_{th1})^2$$

$$= \frac{1}{2} \cdot 350 \cdot 7 \times 10^{-7} \cdot \frac{50}{0.5} \cdot (V_{gs} - 0.7)^2$$

$$= 0.01225 (V_{gs} - 0.7)^2 = 0.5 \times 10^{-3}$$

$$\therefore V_{gs} = 0.902 \text{ [V]}$$

$$gm1 = \mu_n C_{ox} \frac{W}{L} (V_{gs} - V_{th1})$$

$$= 350 \cdot 7 \times 10^{-7} \cdot \frac{50}{0.5} \cdot (0.902 - 0.7) = 4.95 \text{ [mS]}$$

$$ID2 = \frac{1}{2} \mu_p C_{ox} \frac{W}{L} (V_{gs} - V_{th2})^2$$

$$= \frac{1}{2} \cdot 100 \cdot 7 \times 10^{-7} \cdot \frac{10}{0.5} \cdot (V_{gs} - 0.8)^2$$

$$= 7 \times 10^{-4} \cdot (V_{gs} - 0.8)^2 = 0.5 \times 10^{-3}$$

$$\therefore V_{gs} = 1.645 \text{ [V]}$$

$$V_{out} = 3 - V_{gs} = 1.355$$

$$gm2 = \mu_p C_{ox} \frac{W}{L} (V_{gs} - V_{th2})$$

$$= 100 \cdot 7 \times 10^{-7} \cdot \frac{10}{0.5} \cdot (1.645 - 0.8)$$

$$= 1.18 \text{ [mS]}$$

Av = -gm1/gm2 = -4.2

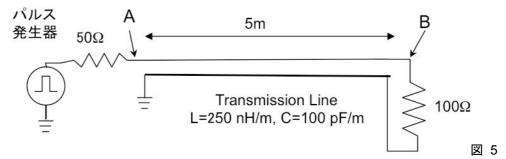

II-C. 図 5 のようなパルス発生器、抵抗、線路(Transmission Line)からなる回路がある。ここでパルス発生器の電圧源は、インピーダンス 0 オームの理想電源とする。

- (a) この線路の特性インピーダンスを求めよ。

- (b) 50 オームの出力駆動能力を持つパルス発生器で信号を発生させた時、この線路を伝わって A 点から B 点に信号が届くまでの伝搬遅延時間を求めよ。

- (c) 遠端での反射係数を求めよ

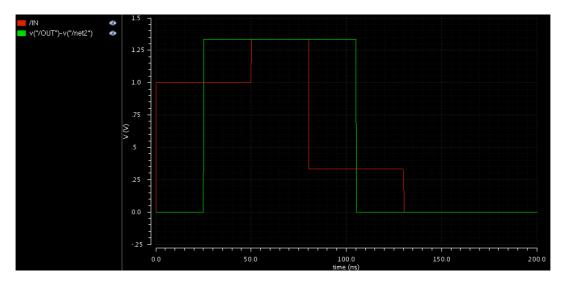

- (d) 時刻 t=0 で波高 2V、パルス幅 80ns のパルスをパルス発生器で発生させた時の、A 点及び B 点で観測した波形をグラフで示せ。

(a)

$$Z = \sqrt{\frac{L}{C}} = 50 \ [\Omega]$$

**(b)**

$$T_d = 5 \times \sqrt{LC} = 25 \text{ [nsec]}$$

(c)

$$R = \frac{100 - 50}{100 + 50} = 0.33$$

- .TRAN 1e-9 200e-9 START=0.0

- .TEMP 25.0

- .INCLUDE "/home/arai/14Lecture/oa/trmodel.inc"

r1 net1 in 50 r0 out net2 100 vin net1 0 PULSE 0 2 100e-12 100e-12 100e-12 80e-9 2e-6 t0 in 0 out net2 ZO=50 TD=25e-9 NL=250e-3 IC=0 , 0 , 0 , 0 .END

\_\_\_\_\_

#### (全員)

II-A. この40年間くらいの間で日本人が発明・開発したエレクトロニクス関連の機器・デバイスについて調べて、あなたが興味を持ったものを1点簡単にまとめて紹介せよ。

III-B. 今回の講義に関して感想、意見がありましたら記して下さい。